Recap: Intel named Sapphire Rapids the fourth generation of Xeon processor in 2019, and disclosed support for DDR5, PCIe 5.0, and in-package memory in the years since. But for all that, they've never committed to a release schedule.

Last week, Intel submitted a Linux kernel change that rounds off the updates they need to run Sapphire Rapids processors with their in-package memory enabled. In theory, then, Intel is preparing to tape out samples for performance testing.

In-package memory, or in this case, ‘on-package’ memory (each of the four core complexes wears a memory die like a little top hat) is an idea to interpose another layer of memory between the L3 cache and system memory. Sapphire Rapids’ in-package HBM2e will be considerably faster than DDR5; with a little back of a napkin math, maybe five or ten times faster.

At this point, though, no one is sure about what that will mean for performance. Intel’s new Linux submission is an update to the i20nm EDAC driver that provides memory error detection and correction reporting -- if anyone had run tests without using that, then their results would’ve been meaningless anyway.

In their submission, Intel discloses that: "A future Xeon processor will include in-package HBM," which is a nice if unexciting confirmation, but they continue by revealing that "the in-package HBM memory controller shares the same architecture with the regular DDR memory controller," which at least implies that it will not be difficult for software to be updated to use in-package memory.

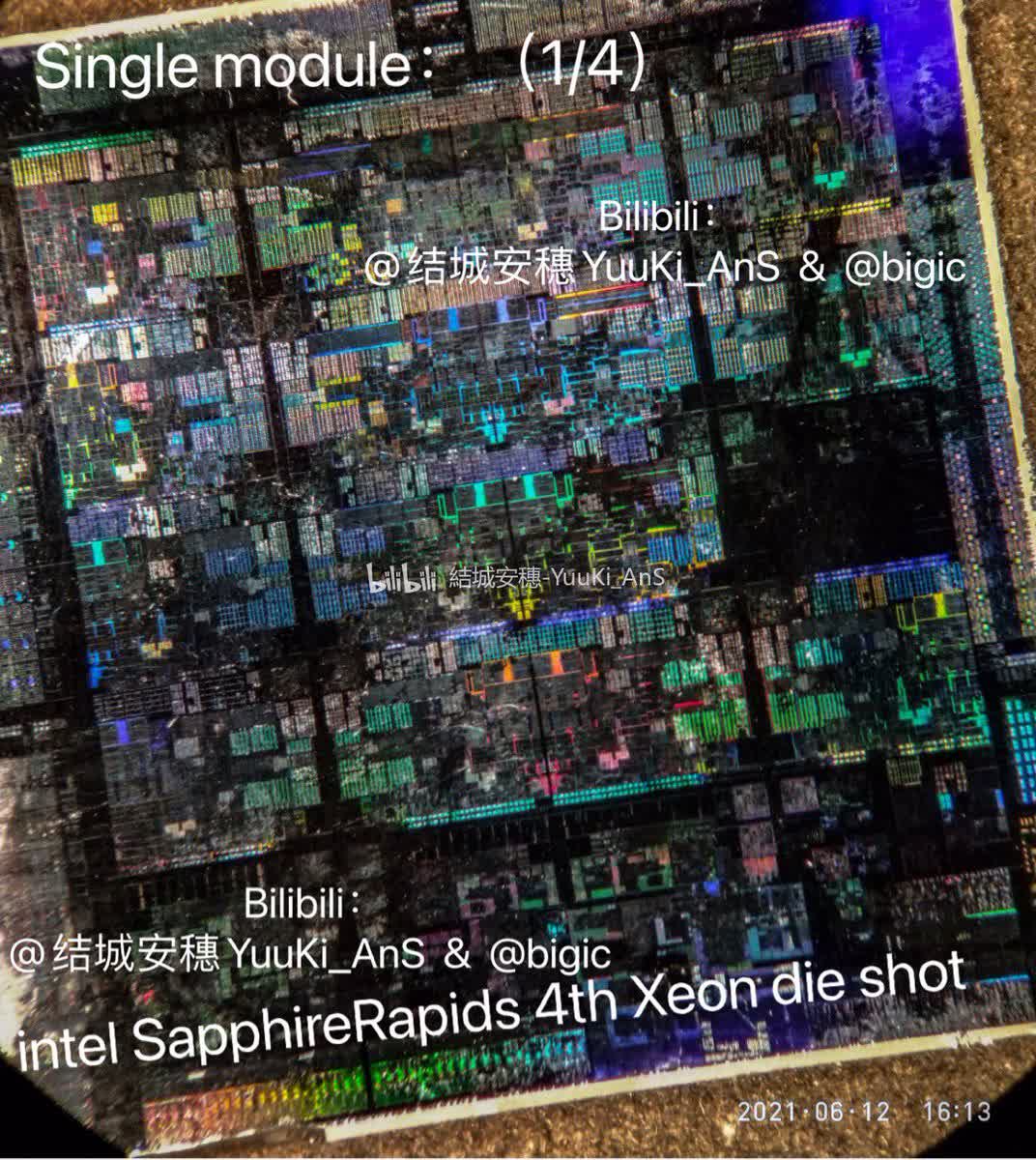

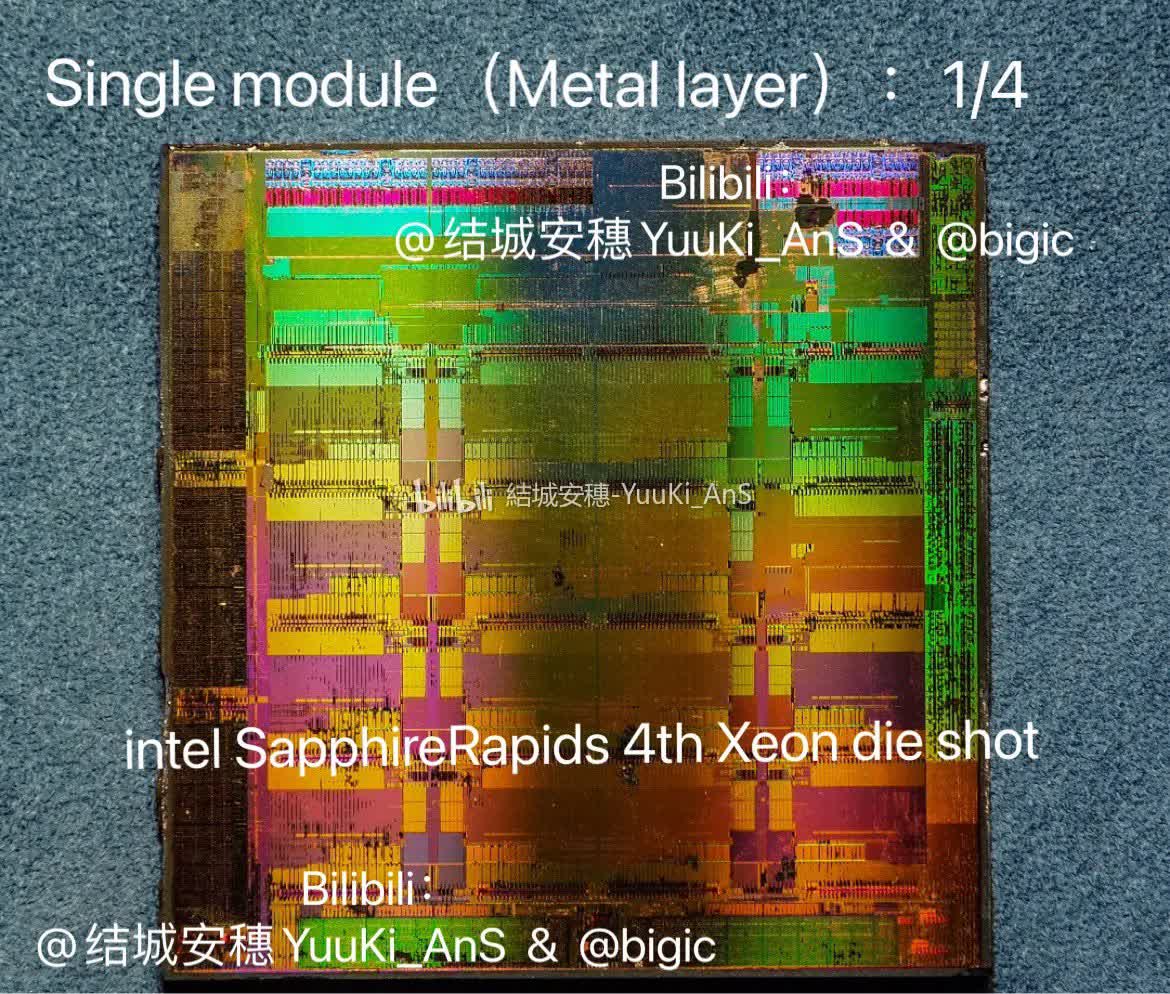

Update:All modules#intel #SapphireRapids pic.twitter.com/KJa7mj5bNq

— 结城安穗-YuuKi_AnS (@AnsYuuki) June 12, 2021

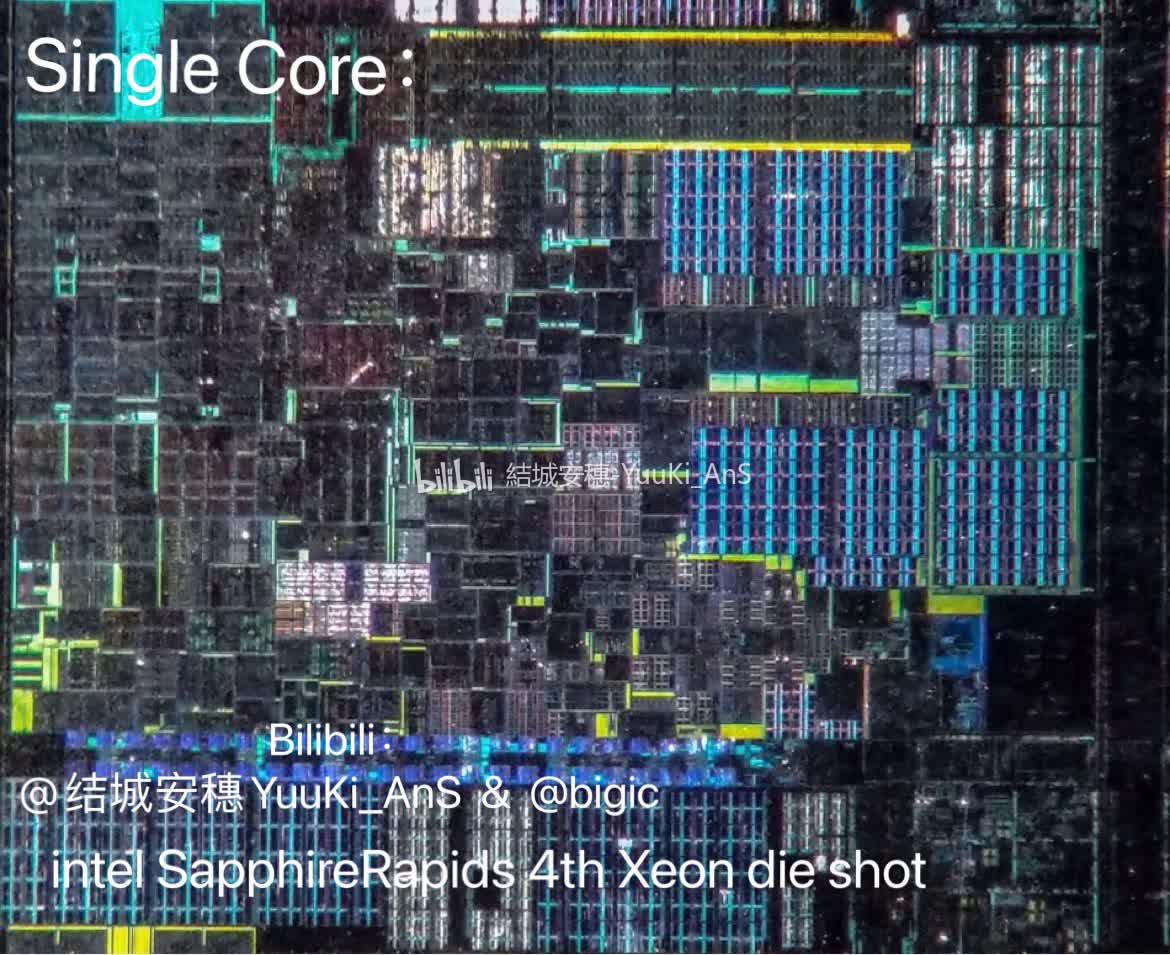

In related news, as you can see above, die shots of Sapphire Rapids are available thanks to the same man that violently tore apart his preproduction sample. The images show that they can’t have 80 cores as was previously thought.

In the images below, the four-by-five grid that was taken to imply the existence of 20 cores is still visible, but we can now see that one of the rows doesn’t contain cores. One of the squares mixed in with the others also seems to contain a different internal structure to the cores, making for a total of 15 cores per core complex, or 60 per quad-complex processor. Rumors say that poor yields are forcing Intel to disable one core per complex, resulting in a usable total of 56 cores.

Masthead credit: Jeremy Zero