Bottom line: That is not a typo: a 2nm-capable fab could cost around $28 billion. In fact, costs throughout the 2nm development and production process will be elevated as the tools will be more complex and the talent needed will be more expensive. One saving grace might be AI-enabled EDA tools that can streamline processes and help reduce costs.

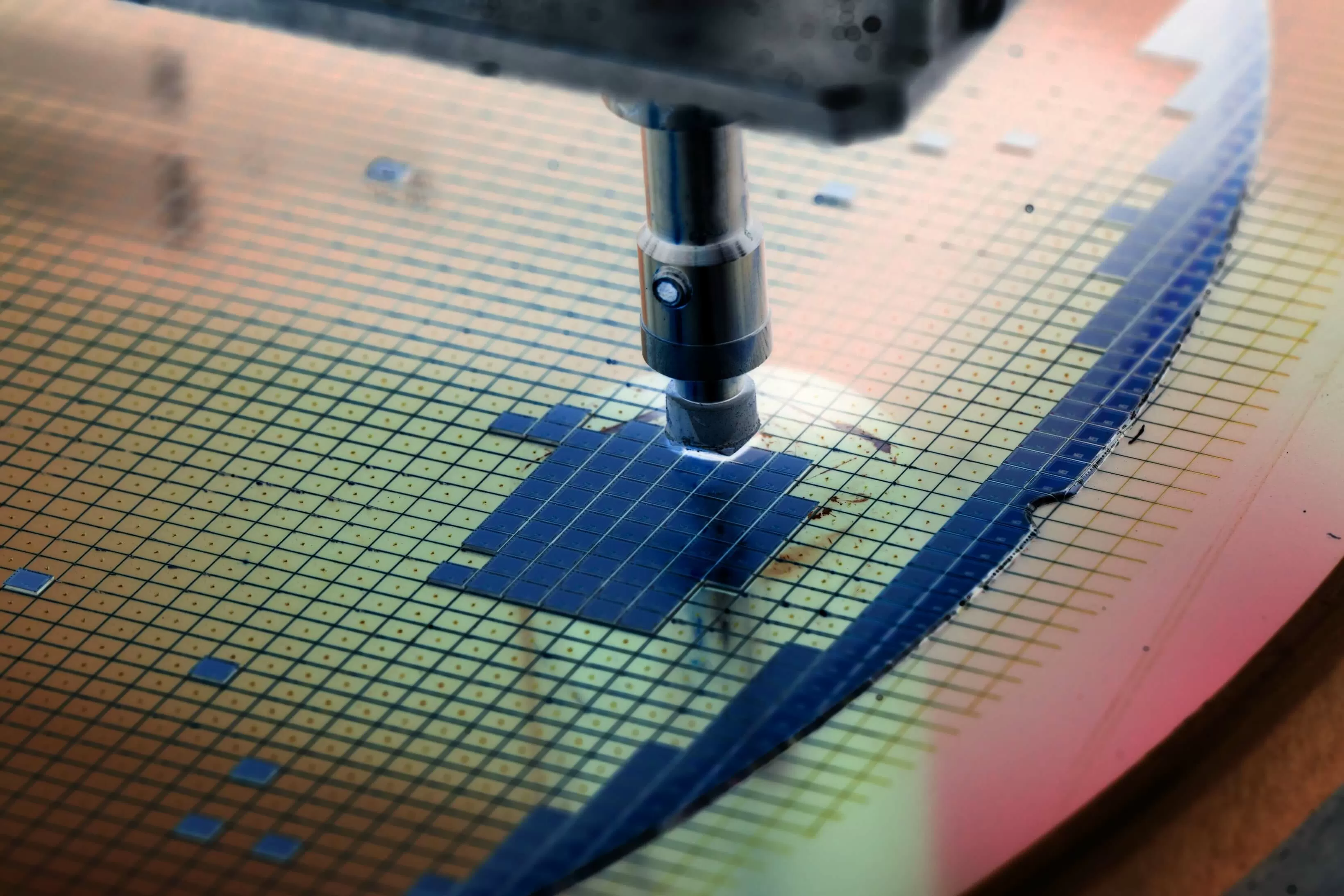

A 2nm-capable semiconductor fabrication plant that has a capacity of 50,000 wafer starts per month, or WSPM, will cost around $28 billion, according to consulting firm IBS. That is $8 billion more than the cost for a 3nm fab and just one illustration of the exponentially higher expenses that firms can expect as the industry moves to the next generation of chips.

To be precise, 2nm chip costs will rise around 50% compared to 3nm processors, IBS says, meaning that companies such as Apple will have to spend $30,000 to process a single 300mm wafer using TSMC's N2 fabrication process when it is introduced in the next few years. Possibly, though, there is some wiggle room in these numbers, potentially bringing down the expected high cost of these chips.

There are in fact numerous approaches that semiconductor companies can take and an array of design decisions they can make during the pre-construction, construction, and operations phases that will materially alter the final cost of the fab.

Also read: How CPUs are Designed and Built

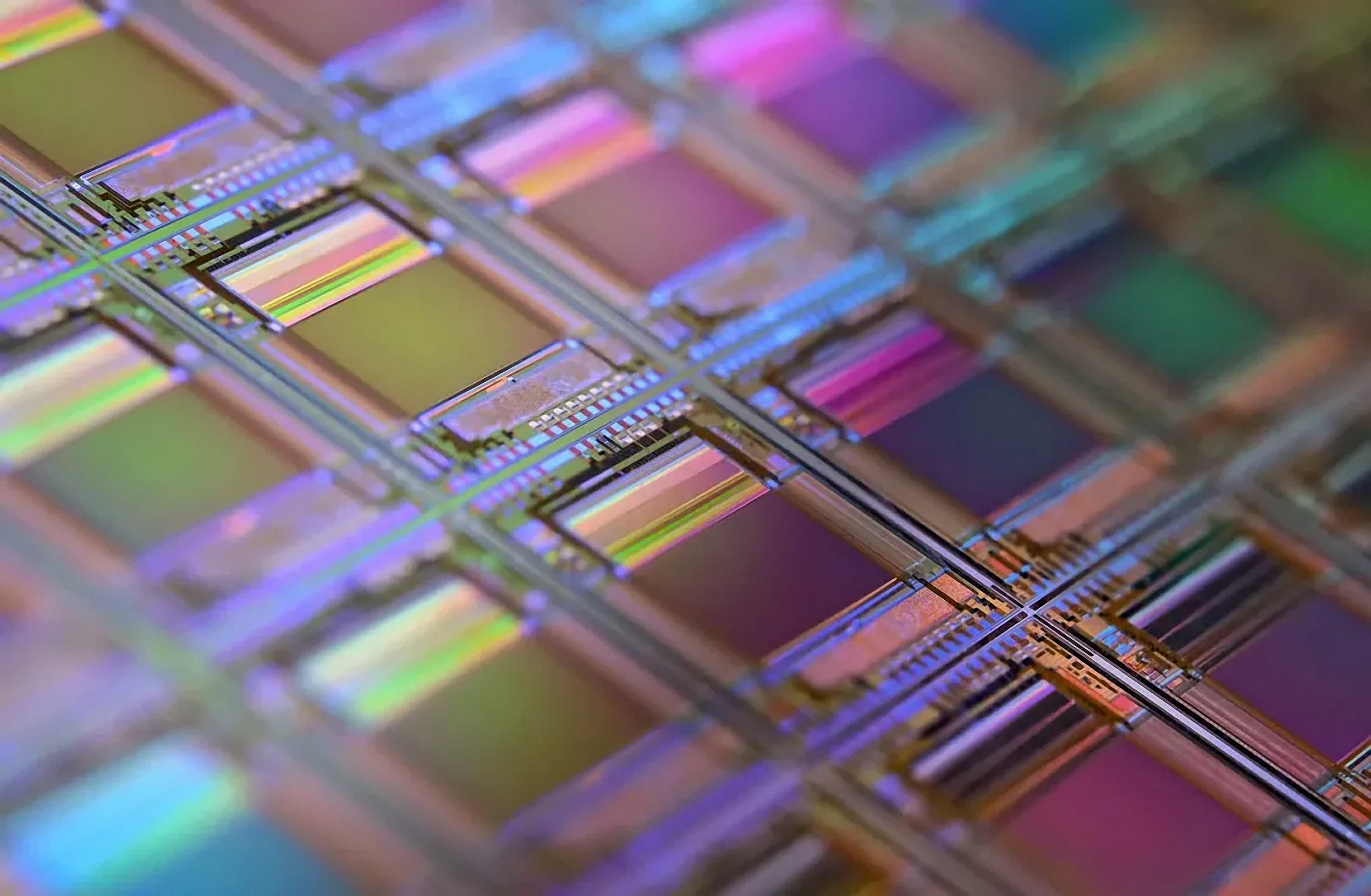

To be sure, the costs of chip development are nothing to scoff at. Software development alone accounts for $314 million and verification is another $154 million, IBS figures show. Also, designing chips at the 2nm node requires specialized talent, which is in short supply. Then there is also the increased use of photolithography, a process used to create the patterns on a chip's surface.

The smaller the features on a chip, the more precise the photolithography process needs to be, thus driving up the cost of the equipment and the materials used in the process. And that 2nm-capable fab that will clock in at $28 billion? Driving the $8 billion cost differential is the increased number of EUV litho tools required to maintain a 50,000 WSPM capacity.

But even IBS acknowledges that there are nuances behind such figures and the evolving landscape of chip design. It has estimated that it can cost a company $725 million to build a sizable 2nm chip from scratch. But that is by a company without pre-existing intellectual property and the reality is many semiconductor companies, particularly startups, pursue more efficient strategies.

IBS also points out that the role of AI-enabled EDA tools is becoming increasingly crucial in chip design, streamlining processes and reducing costs by automating complex design processes and optimizing chip performance.